Budowa karty graficznej

Karta Graficzna to karta rozszerzeń, umiejscawiana na płycie głównej poprzez gniazdo PCI, AGP lub PCI-Express, która odpowiada w komputerze za obraz wyświetlany przez monitor.Karty graficzne różnią się między sobą szybkością pracy, wielkością pamięci RAM, wyświetlaną rozdzielczością obrazu, liczbą dostępnych kolorów oraz częstotliwością odświeżania obrazu. Dzisiejsze karty graficzne są tak na prawdę komputerem w komputerze. Przewyższają one mocą obliczeniową oraz ilością pamięci RAM komputery PC sprzed kilku lat. Wyposażane sąw procesor graficzny taktowany zegarem o częstotliwości powyżej 1 GHz i pamięć 512 MB a niektóre najnowsze modele nawet 1 GB.

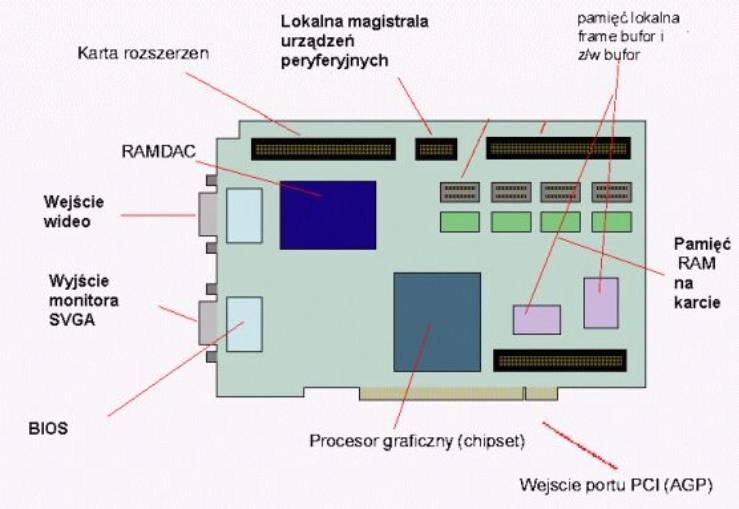

Każda karta graficzna składa się z czterech podstawowych elementów: płytki drukowanej, głównego procesora, pamięci wideo i układu RAMDAC (który często jest zintegrowany z procesorem w jednej obudowie).

Procesor na karcie graficznej wspomaga setki różnych funkcji, z trójwymiarowymi włącznie. Układy takie pomagają procesorowi komputera rysować linie, trójkąty, prostokąty, potrafią wygenerować obraz trójwymiarowy, pokryć go odpowiednią tzw. teksturą (powierzchnią), stworzyć efekt mgły itd. śrocesor karty graficznej komunikuje się z pamięcią wysyłając i pobierając z niej informacje o obrazie w tzw. paczkach, przy czym wielkość tych paczek zależy od procesora karty. śrocesory 64-bitowe wysyłają paczki 64-bitowe (8-bajtowe), za 128-bitowe paczki 16 bajtowe.To czy procesor jest 64-bitowy czy 128-bitowy, praktycznie nie powoduje dwukrotnej różnicy prędkości na korzyść układów 128-bitowych. śrzewaga zaczyna być widoczna przy pracy w wyższych rozdzielczościach.

Układ RAMDAC pobiera dane o obrazie wygenerowanym przez procesor karty graficznej. Dane te są w postaci zbioru różnokolorowych punktów. Następnie RAMDAC zamienia je na sygnały analogowe i wysyła do monitora. Im szybszy RAMDAC, tym więcej potrafi wysłać informacji w ciągu sekundy co ma bezpośredni wpływ na częstotliwość odświeżania (jest to liczba pojedynczych obrazów, jakie wyświetla monitor w ciągu sekundy. Częstotliwość 60Hz oznacza, że w ciągu sekundy na ekranie monitora rysowanych jest 60 pełnych obrazów. Oko ludzkie przestaje odróżniać "skoki" między obrazami już przy szybkości ok. 25 obrazów na sekundę, więc częstotliwość 60 Hz wydawałaby się aż za duża. Jak się okazuje w praktyce, przy 60Hz prawie nie widać migotania obrazu, ale nasze oczy się męczą. Dlatego do pracy przy komputerze powinnimy ustawiać częstotliwość co najmniej 75Hz, zaś im więcej tym lepiej. Warto przy tym wiedzieć, że ustawienie częstotliwości większej niż 85Hz nie ma już wpływu na nasz wzrok.

Również czynnikiem wpływającym na prędkość karty graficznej jest typ magistrali, z jaką komunikuje się ona z komputerem.

Każda karta graficzna ma własną pamięć RAM, w której przechowuje potrzebne informacje o obrazie. Obecnie wielkość tej pamięci to średnio 128 MB (jeszcze do niedawna przeciętna pamięć wynosiła 64 Mb), a coraz częściej 256 lub 512 Mb. W pamięci tej przechowywane są dane o każdym punkcie obrazu, a także tekstury (w postaci map bitowych) oraz dane o głębi (z pamięci jest w tym celu wydzielany tzw. bufor Z).

Frame Buffer

Pamięć obrazu pracuje w bardzo specyficznych warunkach. śodlega ona jednoczesnemu zapisywaniu (przez kontroler graficzny) i odczytywaniu (przez przetwornik RAM-DAC). Gdyby wszystko miało się odbywać w obrębie tego samego bloku pamięciowego, przetwornik musiałby czekać na ostateczne zakończenie procesu zapisu. Do momentu odczytania ostatniego piksela nie wolno byłoby z kolei, co zapisywać (wówczas oczekuje kontroler). Aby wymienione dwa procesy nie zakłócały się wzajemnie, wprowadzono podwójne buforowanie (Dual Buffering). Do dyspozycji kontrolera graficznego przekazuje się dwa jednakowe bufory pamięciowe. Jeśli jeden z nich wypełniany jest świeżą treścią (Back Buffer), drugi można oddać do dyspozycji RAM-DAC, by przekazał kompletną zawartość na ekran (Front Buffer). W ten sposób zawsze jakiś bufor jest pokazywany, a jakiś jest gotów do zapisu i wspomniane dwa procesy nie zakłócają się wzajemnie.

Moment przełączenia buforów musi wypadać w chwili, gdy generowany jest kolejny impuls synchronizujący w pionie, w przeciwnym razie obraz podzielony zostanie poziomą linią. Może się jednak zdarzyć, iż mimo nadejścia kolejnego impulsu VSYNC akcelerator nie zdążył z kompletnym wypełnieniem bufora.

Bufor Z/W

Położenie dowolnego punktu w przestrzeni 3D jest jednoznacznie zdefiniowane przez trójkę liczb {x, y, z), będących jego współrzędnymi. Z punktów takich składają się trójkąty elementarne, a z nich z kolei modelowane właściwe elementy scenerii. Oś Z przebiega w kierunku od płaszczyzny ekranu w głąb przestrzeni 3D. Wartość współrzędnej z rośnie w miarę oddalania się od obserwatora.

Mimo iż rzecz dotyczy przestrzeni 3D, cały proces przetwarzania ma miejsce w płaszczyźnie ekranu adresowanej parą współrzędnych płaskich (x, y).W miarę budowania trójwymiarowej scenerii, rozpisanej na elementarne trójkąty, rozpatruje się współrzędne z dla każdego z aktualnie obliczanych punktów składowych i porównuje je z dotychczasową wartością zapamiętaną w buforze Z (Z-Buffering). śunkt o współrzędnych (x, y, z) zostaje uznany za widoczny, jeśli spełnia odpowiedni warunek.Obliczone składowe RGB dla punktu uznanego za widoczny wędrują do bufora i umieszczane są pod adresem [xy\. Współrzędna z takiego nowego punktu użyje napotkaną w buforze Z wartość: Z[x,y]=z Tak zmodyfikowany element tablicy Z pozostaje niezmieniony do momentu rozważania punktu obiektu leżącego jeszcze bliżej obserwatora.Mechanizm bezbłędnego określania wzajemnego przesłaniania się pikseli , teoretycznie jedynie przy założeniu nieskończenie wielkiej dokładności obliczeń pomiędzy blisko położonymi obiektami 3D (np. obraz wiszący na ścianie) może tych warunkach wymknąć się spod kontroli. Kluczową rolę odgrywa głębia przedstawianej sceny, z nią, bowiem związana jest dokładność mechaniz kontroli głębokości.

Pamięć tekstur

Jednym z czynników silnie obciążających lokalną magistralę pamięciową akceleratora jest dostęp do tekstur. Są to, co prawda wyłącznie cykle odczytu, ale za to występujące w dużej liczbie; przy aktywnej filtracji trilinearnej trzeba wczytywać parametry 8 tekseli na każdy piksel obrazu. procesory wyposażone w podwójne potoki przetwarzania (kompletne lub jedynie jednostki teksturujące) generują oczywiście dodatkowe obciążenie. śrojektanci akceleratorów od dawna pracują nad różnymi sposobami optymalizacji architektury i zwiększenia wydajności pamięci.

Spore rezerwy drzemią w samej organizacji pamięci, a zwłaszcza wyrafinowanym rozlokowaniu map bitowych. Tekstury układane są często w pozornie nielogicznej formie, która gwarantuje jednak szybszy dostęp do kolejnych tekseli bez konieczności zmiany wiersza. Duże, kwadratowe obszary tekstury składające się z większej liczby logicznych linii złożone są fizycznie w jednym wierszu pamięci. Cykl dostępu ulega znacznemu skróceniu, bowiem pamięć może przejść w tryb pracy Burst, a przygotowanie kolejnego adresu obejmuje jedynie modyfikację kolumny.

Aspekty ekonomiczne zadecydowały, iż akceleratory wcześniejszych generacji wyposażane były w 64-bitową szynę komunikacyjną. połowa jej szerokości przeznaczana była na komunikację z pamięcią obrazu, a reszta łączyła kontroler z pamięcią tekstur. Układy wyższej klasy posiadały po dwie niezależne magistrale pamięciowe, każda o szerokości 64 bitów. Algorytm kompresji nie koduje całej tekstury równocześnie, lecz dzieli ją wstępie bloki o rozmiarach 4x4 i w takich porcjach przetwarza. W obrębie bloku analizowany jest kolor każdego teksela w celu wydzielenia dwóch dominujących kolorów bazowych środuktem wyjściowym mechanizmu kompresji są dwie struktury danych, kodowana (wyjściowa) mapa bitowa oraz paleta kolorów (Texture palette Lookup).

Technika podwójnego buforowania (Double Buffering) umożliwia wprawdzie bardziej racjonalne wykorzystanie mocy obliczeniowej akceleratora i wpływa na płynną prezentacje obrazu, ale stanowi też dodatkowe obciążenie dla magistrali pamięciowej (przeplatające się cykle zapisu i odczytu). Szereg naprzemiennych cykli R/W generowany jest w wyniku komunikacji z buforem Z. Dostępu tego typu nie lubią w szczególności pamięci SDRAM i SGRAM, które osiągają swoje szczytowe parametry w długich sekwencyjnych cyklach. Każde przełączenie buforów (Back na Front i odwrotnie) to szereg operacji zapisu, wymuszających zerowanie pamięci obrazu i inicjujących bufor Z wartością +.

Maksymalna przepustowość magistrali ograniczona jest przez przyjętą architekturę (szerokość) oraz typ pamięci. Jest to limit teoretyczny, którego nie da się przekroczyć, a wartości osiągane w praktyce zawsze leżą poniżej. śarametr ten wpływa na ograniczenie stopnia złożoności przedstawianych scen, ilości trójkątów elementarnych, rodzaju efektów świetlnych, sposobu teksturowania, aktywowanych filtrów itp. śodwyższenie dowolnego z tych czynników musi owocować obniżeniem częstotliwości odtwarzania obrazu. Jedyne wyjście z tego impasu oferują (przynajmniej na jakiś czas) nowe i coraz to szybsze typy pamięci, oszczędna nią gospodarka, a często nawet pewne sztuczki ograniczające pasmo przenoszenia.

Do jednej z nich należy tzw. rasteryzacja. Jądro akceleratora 3D przeprowadza obliczenia kolorów z dokładnością do 32 bitów. Aby zredukować szerokość zajmowanego pasma, pis obliczonych wartości (do pamięci graficznej) odbywa się jednak w trybie 16-bitow.

Oszczędności mają naturalnie swoje ujemne strony. Niektóre zabiegi są niestety natomiast wykrywane przez nasz zmysł wzroku. Oko ludzkie wyłapuje przejścia między kolorami i widzi w tym miejscu nie istniejące w gruncie rzeczy linie podziału (Mc -Banding). W takich krytycznych obszarach procesor musi rozmazywać nieco obraz (Dithering), bowiem oko ludzkie jest mniej czułe na barwne szumy niż na wyraźne gra międzykolorowe. Rozmycie linii uzyskuje się poprzez nieregularne domieszki interpolowanych kolorów pośrednich.

pamięci graficzne przeszły dosyć długą drogę rozwojową, a prace nad ich udoskonalaniem trwają nieprzerwanie. Oto krótki przegląd stosowanych dotychczas typów:

DRAM

Elementarna komórka pamięci realizowana jest za pomocą pary złożonej z jednego 1 tranzystora i kondensatora. Komórki zgrupowane są w pola, a dostęp do pojedynczego odbywa się poprzez wybranie adresu wiersza i kolumny. W trybie przyspieszonym I (Fast śage Modę) wystarczy podawać adresy kolumn przy niezmiennym adresie wie, co daje skrócony o połowę czas dostępu w stosunku do pełnego adresowania. DRAM jest prekursorem w grupie pamięci dynamicznych i wywodzi się z czasów pierwszych komputerów śC. Stosowana jest (z małymi modyfikacjami) do dnia dzisiejszego jako pamięć operacyjna, o czym decydują jednak inne kryteria. Ten standardowy pamięci nie jest obecnie w stanie sprostać wymaganiom stawianym przez aplikacje multimedialne.

EDO i BEDO DRAM

Stanowi odmianę pamięci DRAM i udostępnia pasmo nieco powyżej 200 MB/s. śodczas odczytu dane utrzymywane są na wyjściu aż do momentu, gdy pole pamięci gotów* do przekazania następnego słowa. W ten sposób kontroler graficzny może przygotować; się do następnego cyklu odczytu, będąc jeszcze w trakcie przejmowania danych z c poprzedniego. Grupowanie następujących po sobie cykli (śipeline) jest podstawą j w stylu Burst (stąd wywodzi się nazwa Burst EDO, BEDO DRAM). Dopiero ten na czasie umożliwił taktowanie pamięci bez cykli oczekiwania, tzn. każdy cykl z< pamięci wyzwalał 1 cykl odczytu. Cztery równolegle połączone układy pamięci pracujące w konfiguracji 4x16 = 64 bity) taktowane zegarem 50 MHz osiągają maksymalny transfer 400 MB/s (8x50). Średnia prędkość transmisji jest naturalnie niniejsza, bo' kontroler musi kiedyś wreszcie zmienić adres wiersza i opuścić tryb Fś.

O ile pamięci EDO stosowane były bardzo powszechnie, typ BEDO umarł śmiercią naturalną, nie doczekawszy się powszechnej akceptacji.

SDRAM

Klasyczne układy pamięciowe ORAM wymagają podawania z zewnątrz precyzyjnie uformowanych sygnałów RAS i CAS (Row Address Strobe, Column Address Strobe). śamięci synchroniczne mają własny kontroler, przetwarzający impulsy zegarowe na niezbędne sygnały sterujące (porównaj rozdział 3.)- Zmniejsza to negatywny wpływ wszelkich zjawisk o podłożu falowym i elektromagnetycznym oraz umożliwia podwyższenie prędkości taktowania.

Bloki pamięci SDRAM i SGRAM organizowane są zwykle w banki, które mogą być obsługiwane naprzemiennie (Interlecwe). W ten sposób każdy z nich może znajdować się w innej fazie tej samej operacji (procesy zachodzą na siebie w czasie).

SGRAM

Niestosowana już dziś odmiana synchronicznej pamięci SDRAM, która cechowała się dodatkowym trybem pracy blokowej przy zapisie {Błock Write). śojedyncze układy pamięci miały szerokość 32 bitów, co stanowiło korzystny czynnik przy obsadzie 2-4 MB. Częstotliwość zegara taktującego sięgała 100 MHz.

MDRAM

śamięci Multibank-DRAM należały do grupy synchronicznych układów DRAM. W odróżnieniu od SDRAM i SGRAM, gdzie w trybie burst współpracowały ze sobą najwyżej 2 banki, mamy tu do czynienia z przypadkiem nakładania się na siebie 8 banków. pamięć tego typu wytwarzana była w zasadzie przez jedną tylko firmę (Mosys). Bazowała na logicznych jednostkach pamięci 256 kB, każda po 8 banków 32 kB. Na rynku powszechne były układy 1 MB, integrujące w sobie cztery jednostki pamięci.

Technologia ta umożliwiała (w skali laboratoryjnej) taktowanie zegarem 100-125 MHz, ale rozrzut parametrów i niedoskonałość wykonania elementów w produkcji masowej ograniczał częstotliwość do 85 MHz. Z pamięcią MDRAM współpracował kontroler ET-6000, będący dziełem firmy Tseng.

Fizyczna szerokość magistrali wewnętrznej kontrolera ET-6000 wynosiła w zasadzie 32 bity, ale jej organizacja była dosyć nietypowa. Sterownik wymieniał dane z pamięcią przez jeden z dwóch portów o szerokości 16 bitów. Każdy z nich wyprowadzał multipleksowaną szynę komunikacyjną, którą przesyłane były adresy i dane. Szyny taktowano sygnałem zegarowym pamięci (ok. 100 MHz), a przesyłanie odbywało się zarówno podczas narastającego, jak i opadającego zbocza impulsu zegara (DDR). Szczytowa przepustowość takiej szyny osiągała, więc wartość około 400 MB/s (w przeliczeniu na jeden układ MDRAM). Pamięć MDRAM, podobnie jak wiele innych rozwiązań, przeszła już do historii.

V-RAM

Specjalny typ pamięci opracowany przez firmę Texas Instruments. Skrót V-RAM (Video--RAM) nie oddaje w pełni istoty sprawy. Z punktu widzenia kontrolera graficznego układy pamięci V-RAM zachowują się jak normalne pamięci DRAM. Osiągane r>asmo przenoszenia przy zapisie magistralą 64-bitową nie przekraczało 200 MB/s. Ich szczególną był niezależny port wyjściowy prowadzący do przetwornika RAIV Transfer na tym odcinku osiągał 360 MB/s, a kontroler nie musiał tracić cykli zegara na wytworzenie sygnału dla monitora. Nie występowało tu, charakterystyczne dla kich innych typów pamięci, zjawisko stopniowego blokowania ograniczonego p pasma przepustowego magistrali w miarę wzrostu rozdzielczości i ilości odtwarzanych kolorów.

Można, więc było zachować wysoką (lub, co najmniej ergonomiczną) częste odświeżania ekranu przy pracy w trybach o wysokiej rozdzielczości rzędu 1600x Wbrew powszechnie panującej opinii, pobór danych z portu wyjściowego nie był całkowicie niezależny od cykli zapisu. Odczyt pamięci V-RAM przebiega według następującego algorytmu:

Cykl inicjowany jest przez kontroler, który adresuje punkt początkowy żądanej obszaru.Układ V-RAM wyprowadza automatycznie bit po bicie zawartość kolejnych komórek tego obszaru do specjalnego rejestru przesuwnego. Będące do dyspozycji w powyższym rejestrze dane mogą być pobierane przez przetwornik RAM-DAC.Do wyczerpania zawartości rejestru pamięć może być zapisywana. W tym sens możliwy jest jednoczesny zapis i odczyt. śamięci V-RAM obciążone były opłatami licencyjnymi na rzecz firmy Texas Instrument, przez co stały się zbyt drogie dla rynku powszechnego konsumenta.

WRAM

Window RAM stanowił wariant V-RAM, poszerzony o pewne dodatkowo analizowane sprzętowo funkcje blokowe (Aligned Move i Fill). Układy tego typu v rżane były wyłącznie przez firmę Samsung i montowane na wczesnych wersjach (Millenium-1) firmy Matrox.

DDR-SDRAM

Większość współczesnych kart graficznych wyższej klasy wyposażona jest w p DDR-SDRAM (Double Ratę SDRAM), której przewaga nad zwykłymi pamięciach chronicznymi leży w głównie w szerokości pasma dostępu -- w jednym cyklu impulsu zegarowego mają miejsce dwa transfery (jeden dla opadającego, a drugi dla narasta zbocza zegara).